How to Implement DDR4

DDR4 succeeded DDR3 as the next generation of synchronous DRAM (SDRAM) software. DDR4 offers several improvements over its predecessor, including faster download speed, higher DIMM capacities, enhanced data integrity and power efficiency, and overall improved performance.

Compared with DDR3, the DDR4 PCB design consists of several physical changes. First, DDR4 has 288 pins as opposed to DDR3’s 240, and each data pin can achieve transfer rates exceeding 2 Gbps. What’s more, DDR4 units curve slightly at the bottom to improve strength and stability during installation.

DDR4 offers a 50% performance increase and can achieve speeds of up to 3,200 MTs. Tests also reveal that DDR4 can consume up to 40% less power, requiring 1.2 volts per DIMM compared with DDR3’s 1.5 volt and 1.35 volt.

Other improvements include features that improve reliability such as cyclic redundancy checks, on-chip parity error detection, and improved signal integrity.

DDR4 PCB Layout Design Guidelines

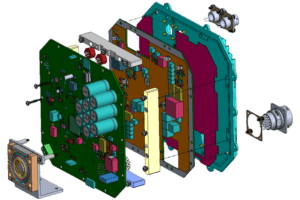

PCB layouts for DDR4 designs require careful planning to get the most out of your hardware. They must also meet the rigorous demands of today’s memory requirements. Several factors, including critical connections and space allocation, govern the initial design stages, as designers must satisfy design specifications and routing topologies for successful implementation.

PCB layouts for DDR4 designs require careful planning to get the most out of your hardware. They must also meet the rigorous demands of today’s memory requirements. Several factors, including critical connections and space allocation, govern the initial design stages, as designers must satisfy design specifications and routing topologies for successful implementation.

Circuit boards must follow routing and PCB best practices to effectively manage data. Failing to do so can result in several issues including radiated emissions and susceptibility. You should also employ appropriate techniques for data ranges between 1.6 and 3.2 Gbps, large-scale fan-outs, and high edge rates to maintain low bit error rates. Lack of proper design technique can compromise signal integrity and lead to crosstalk resulting in excessive jitter.

DDR4 Length and Spacing Rules

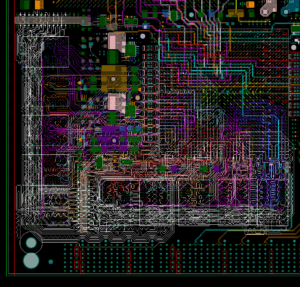

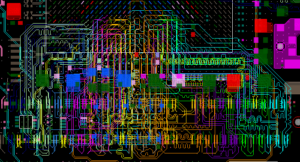

Proper memory chip use and DIMM connector placement enables the best possible path for routing. DDR4 SDRAM requires shorter routes and proper spacing for peak timing and optimal signal integrity. Implementers should utilize pin swapping in appropriate signal groups, and avoid routing signal layers next to each other, routing signals over voids, and reference plane splits.

Workers should rout memory interface signals between the appropriate GND or power layers when possible. You can reduce or eliminate transmission velocity differences by routing the DQ, DQS, and DM signals in the same byte-lane group on the same layer.

Due to the longer propagation delay of the clock signal compared with the DQS signal, the clock signal trace usually requires a length longer than the longest DQS trace in dual in-line memory modules.

You need to keep in mind that every board stack-up is different, therefore every spacing requirement is different. A field solvers should be used to establish crosstalk lower than -50dB between critical signals.

Clock to DQS has no length requirement, but clock to command/control/address does have a length requirement. How much longer to run it depends on Dk of the material and the loading at each SDRAM.

As an example, the following is a good starting point for internal layers, however a field solver is required to determine the appropriate line widths and spacing requirements for a specific board stack-up.

- Within a data byte lane, 3H spacing between data bits/mask and 4H mils spacing to the strobe(s). (H = spacing from trace to the closest reference plane) Note that depending on the configuration, some byte lanes will not have a mask but will have two strobe pairs. 5H mils spacing to non-DDR4 nets.

- Within the address/command/control, 3x mil spacing within the group, 4x mils to any other DDR4 related net and 5x mils to non-DDR4 nets.

- Spacing to DDR4 clocks is 4x mils spacing and 5x mils spacing to non-DDR4 related nets.

Data Lanes Reference Ground

Data Lanes Reference Ground

Address and Control reference ground OR power depending on controller. DIMMS have address and control reference power. On board BGA’s rarely have the address and control reference power.

DDR4 Layer Assignments

DQS/DQ/DM nets can be assigned to any internal stripline layer in a stack-up. Clock and Address/Command/Control should be routed on layers closer to the SDRAM to minimize via coupling. Address/Command/Control SDRAM vias should have added vias connected to GND (aka “shadow vias”) at each SDRAM to minimize via coupling.

Choose Freedom CAD for Your DDR4 Implementation Needs

Freedom CAD Services Inc. provides one-stop solutions for all your DDR4 PCB design and layout needs. Our services complement your engineering team’s capabilities, building PCB designs of unmatched precision and quality.

Data Lanes Reference Ground

Data Lanes Reference Ground